Fetching a word from the memory

- CPU transfers the address of the required information to MAR from where it is transferred through Address Bus to Memory

- In the same time CPU uses it’s control lines of memory bus to indicate that a read operation is required

- After issuing this request CPU waits until it receives a feedback from the memory indicating that the requested function has been completed

- This is done using another control signal on the memory bus, referred to as Memory Function Completed (MFC)

- The memory sets this signal to 1 to indicate that the contents of the specified location in the memory have been read and are available on the data lines of the memory bus and thus available for use inside the CPU

- This completes the memory operation

Asynchronous Transfer

- The transfer mechanism where one device initiates the transfer and waits until the other device responds is called Asynchronous transfer.

- This mechanism enables transfer of data between two independent devices that have different speed of operation

Fetching a word from the memory

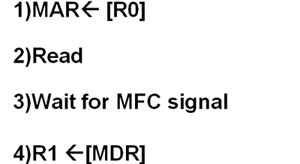

Example: Assume that the address of the memory location to be accessed is in register R0 and data is to be loaded into register R1. Following sequence of operations are used .

Duration of step depends on Memory access time. During this time CPU can carry out tasks that do not require MAR and MDR like ……

SINGLE BUS STRUCTURE << Previous

Next >> Synchronous Transfer

Support us generously: contact@lessons2all.com

Our aim is to provide information to the knowledge seekers.

.jpg)